Details

Part No: 04B-340

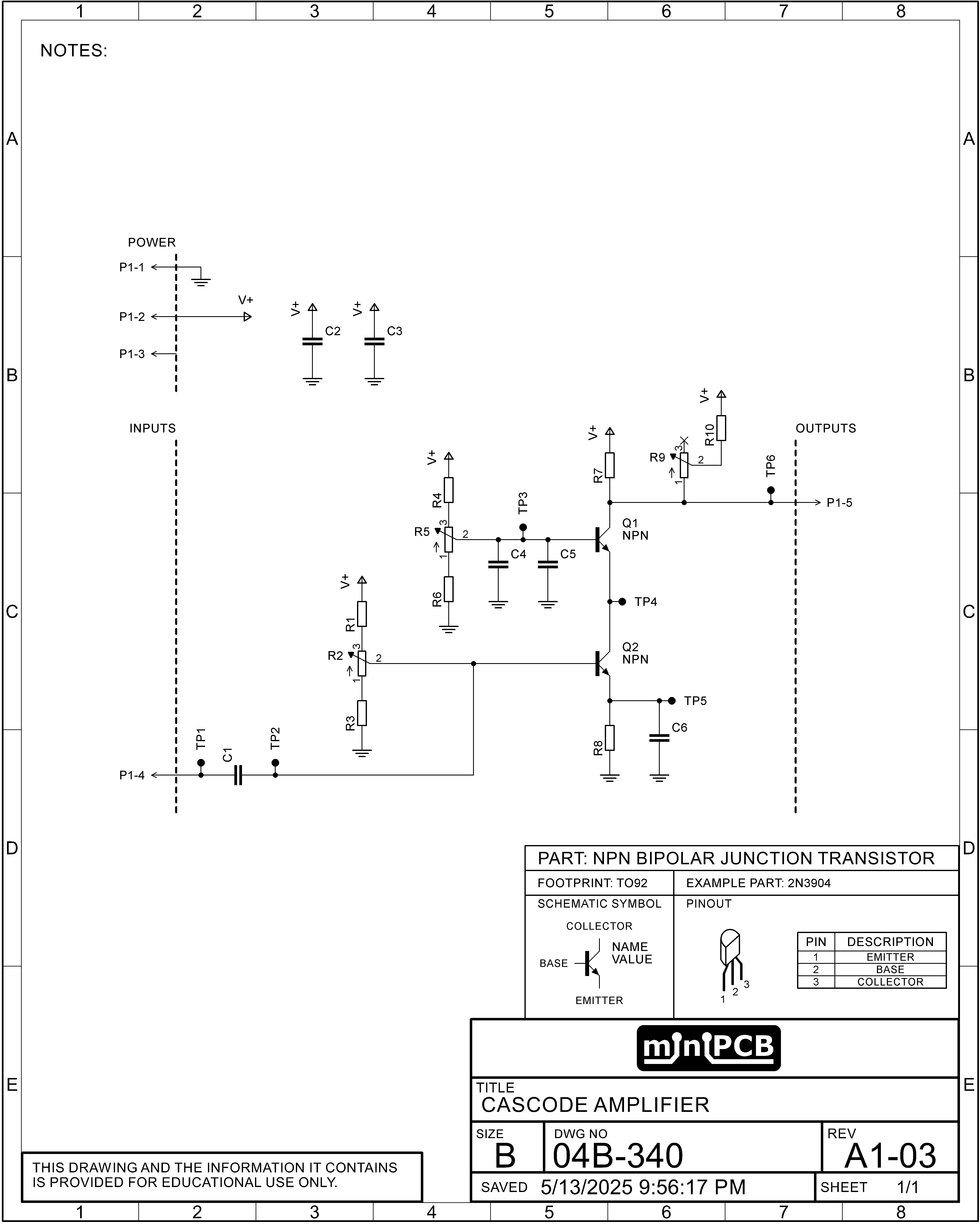

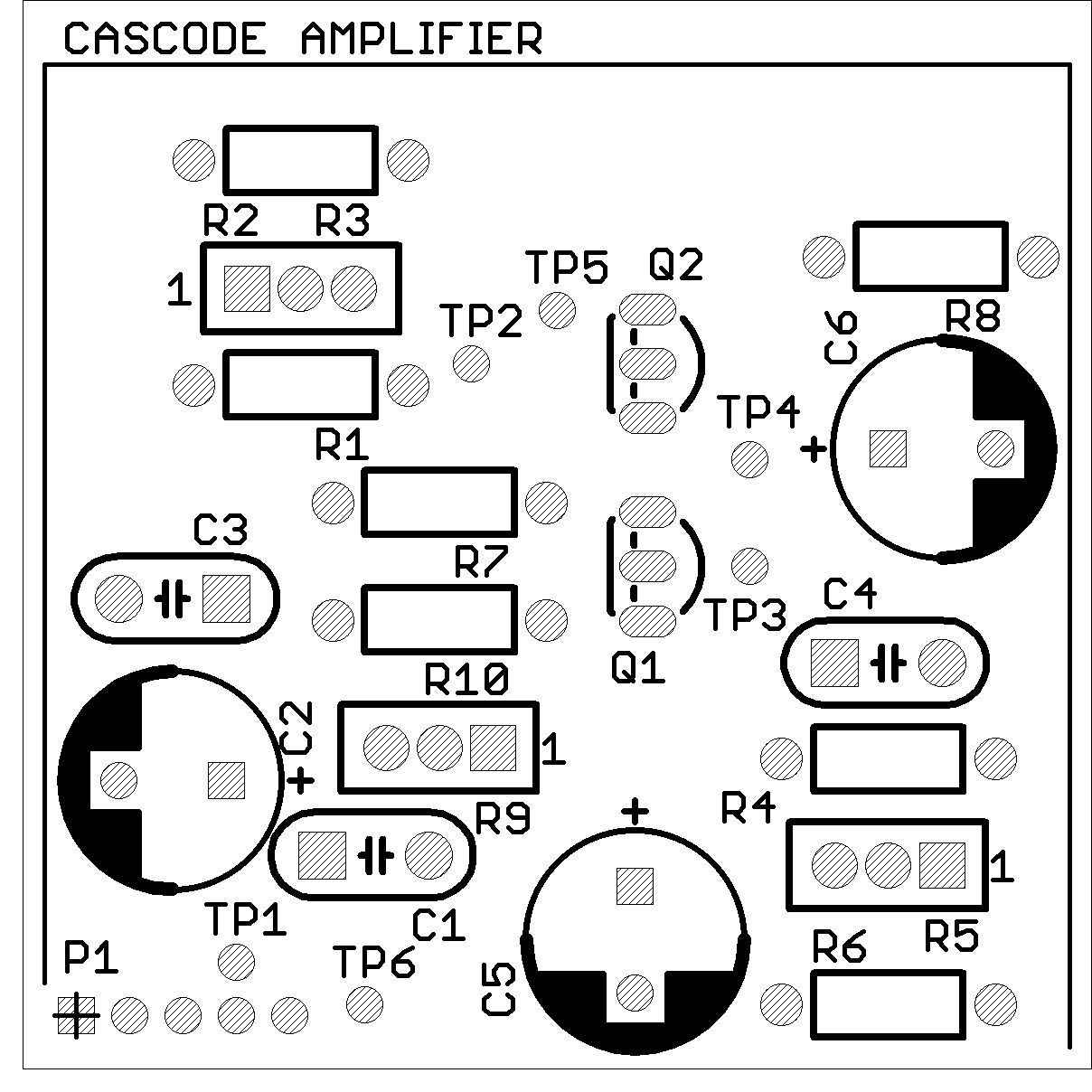

Title: Cascode Amplifier

Board Size: 50 x 50 mm

Pieces per Panel: 4

Panel Size: 100 x 100 mm (V-scored)

Videos

Schematic

Layout

Downloads

Additional Resources

Revision History

| Date | Revision | Description | By |

|---|---|---|---|

| 2025 | - | Initial release | N. Manteufel |